極小半導体デバイスの性能シミュレーション

ナノレベルに達した半導体デバイス

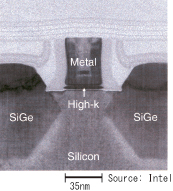

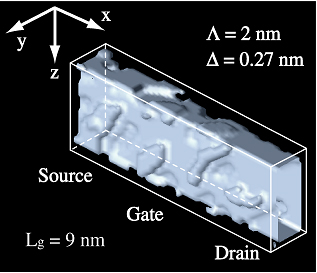

携帯電話、パソコン、ゲーム、デジタルカメラ等、現代社会において、ほぼ全てのエレクトロニクス機器に半導体デバイスが用いられており、これらの機器の性能は半導体デバイスの性能で決まると言っても過言ではありません。では半導体デバイスの性能を左右する要因とは何でしょうか。代表的半導体デバイスであるMOS型トランジスタを例にとった場合、小型化が最も重要になってきます。小型化により、消費電力を抑制し、回路の集積度を上げ、スィッチング速度を高めることができます。そのため現在では、ウィルスより小さい半導体デバイス(ゲート長=約35nm)が出現するに至っています。

このようなナノレベルのサイズになると、既存デバイスの性能を補正しながら次の世代のデバイスを設計するという従来からの手法が通じなくなります。そして、全く新しい視点に立ったシミュレーションにより量子的な挙動も考慮しながら、デバイス設計を進めていく必要があります。

- 森 伸也 准教授

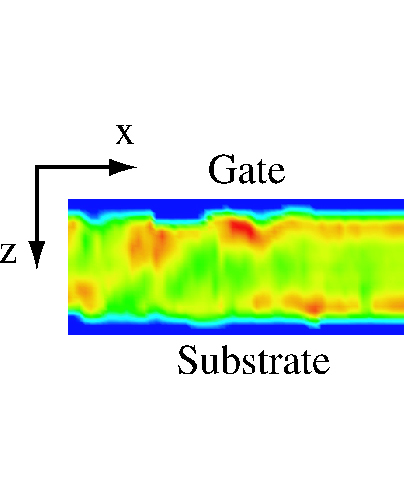

| ウィルスよりも小さい半導体デバイス | ナノレベルのデバイス表面 | ナノレベルのデバイスにおける 電子密度分布 |

||

|

|

|

SQUATS※半導体デバイスシミュレーション

上述のような背景のもと、私は従来からのシリコンMOS型トランジスタを極小化した場合のシミュレーション、さらには新規材料あるいは新構造のデバイスを対象にしたシミュレーションを行っています。新世代MOSFETとして様々なものが提案されているわけですが、その中でどれが有望か評価を下すためにはシミュレーションで性能評価を行う必要があります。

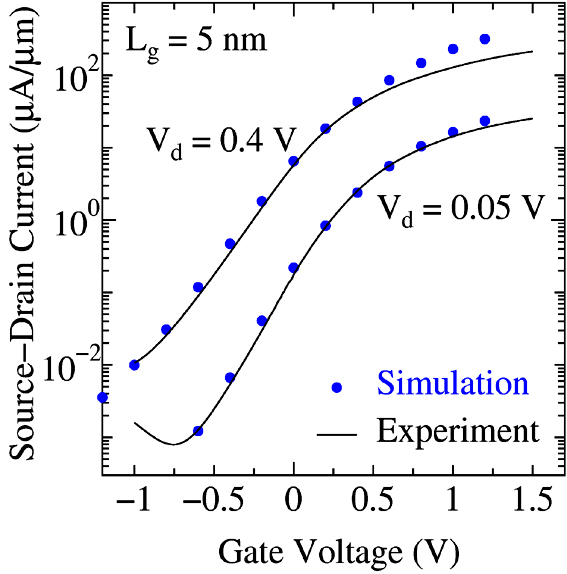

我々は量子力学をよりどころとしてデバイスシミュレーションを行うわけですが、実は量子力学だけではシミュレーションをすることはできません。非平衡統計力学理論を組み合わせる必要があるのですが、その理論自体が完成しているわけではないのです。ですから、シミュレーションを始める前提として、非平衡統計力学のどの理論を信じるかで出発点が違ってしまいます。我々の場合は、非平衡グリーン関数法をよりどころとした手法でシミュレーションを行っています。今は主にシリコンデバイスを対象にシミュレーションを行っていますが、シリコンのいいところは実際に小さなデバイスを作ることができるので、机上だけのシミュレーションで終らないところです。実際にシミュレーション結果と実験値を比較することができるわけです。右のグラフはゲート長=5nmのシリコンMOSトランジスタにおける比較実験結果ですが、シミュレーション値は実験値とよく一致しており、我々のシミュレーション手法の信頼性の高さが証明されたわけです。

※SQUATS : STARC Quantum Transport Simulator

- 電流・電圧特性の

シミュレーション値と

実験値との比較

新世代のデバイス開発の針路を探る

シリコンを材料としたデバイスの場合、その性能や製造コスト等で小型化の限界が見えてきています。新しいデバイス構造や新材料によるデバイス開発を進めなければなりません。しかし、あまりにも選択肢が多いため、いまだに革新的なデバイスの姿は絞り切れていないのが現状でしょう。我々は独自のシミュレーション手法を駆使して、デバイスイノベーションの針路を示すことを目標に研究を続けていきたいと考えています。

物理という学問は、最初に出発点を決めればわりとスムーズに進むんです。何を信じて進むかが、研究者によって意見の分かれるところですね。

- 森 伸也 准教授